Difference between revisions of "Ox64"

Jump to navigation

Jump to search

(Created page with "400px|thumb|right|The Ox64 The '''Ox64''' is a RISC-V based Single Board Computer powered by Bouffalo Lab BL808 C906 64-Bit RISC-V CPU, 32-Bit CPU, embedded 64MB PSRAM memory and build-on 3 radio RF (Wifi, BT, Zigbee). It provides breadboard friendly format factory, MicroSD Card slot, USB 2.0, and many other peripheral interfaces for makers to integrate with sensors and other devices. 600px| == Software releases == === Quic...") |

(Update NuttX and OpenAMP) |

||

| (26 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

[[File:Ox64_board.jpg|400px|thumb|right|The Ox64]] | [[File:Ox64_board.jpg|400px|thumb|right|The Ox64]] | ||

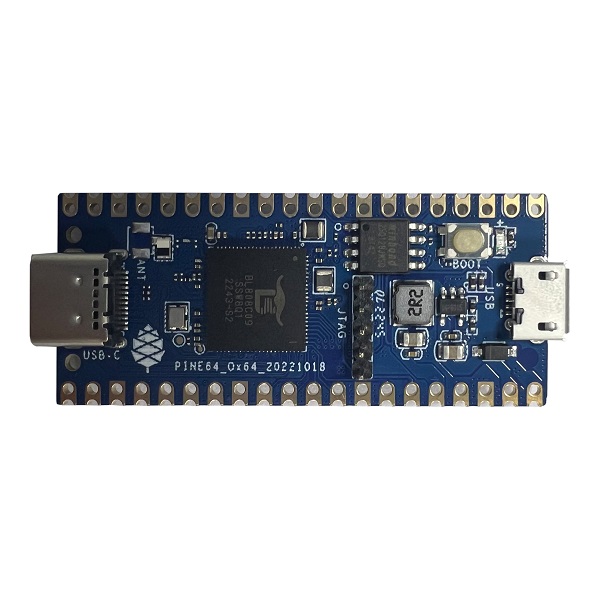

The '''Ox64''' is a RISC-V based Single Board Computer powered by Bouffalo Lab BL808 C906 64-Bit RISC-V CPU, 32-Bit CPU, embedded 64MB PSRAM memory and build-on 3 radio RF (Wifi, BT, Zigbee). It provides breadboard friendly | The '''Ox64''' is a RISC-V based Single Board Computer powered by Bouffalo Lab BL808 C906 64-Bit RISC-V CPU, 32-Bit CPU, embedded 64MB PSRAM memory and build-on 3 radio RF (Wifi, BT, Zigbee). It provides breadboard friendly form factor, MicroSD Card slot, USB 2.0, and many other peripheral interfaces for makers to integrate with sensors and other devices. | ||

[[File:RISC-V.png|600px|]] | [[File:RISC-V.png|600px|]] | ||

== Software | == Software Releases == | ||

=== Quick Links to the Source of OS Images Build === | === Quick Links to the Source of OS Images Build === | ||

| Line 11: | Line 11: | ||

OS images are still in '''alpha build''' which are only fit for board bring up and testing purposes. | OS images are still in '''alpha build''' which are only fit for board bring up and testing purposes. | ||

* [https://github.com/bouffalolab/bl808_linux Linux for BL808] | |||

* [https://wiki.pine64.org/wiki/File:Linux_BL808.pdf Installation Instructions for Linux on BL808 (Chinese)] | |||

* [https://wiki.pine64.org/wiki/File:Linux_BL808_en.pdf Installation Instructions for Linux on BL808 (English Auto-Translation)] | |||

* Toolchain: | |||

** elf_newlib_toolchain/bin/riscv64-unknown-elf-gcc (Xuantie-900 elf newlib gcc Toolchain V2.2.5 B-20220323) 10.2.0 | |||

** linux_toolchain/bin/riscv64-unknown-linux-gnu-gcc (Xuantie-900 linux-5.10.4 glibc gcc Toolchain V2.2.4 B-20211227) 10.2.0 | |||

** cmake version 3.19.3 | |||

=== Software Development Kits === | |||

* [https://github.com/bouffalolab/bl_mcu_sdk BL808 MCU SDK] | |||

* [https://app.box.com/s/aeqkvd6ddtixf4vb2lyuslpu0vu3498y BLDevCube Flashing Tool for Windows, macOS and Ubuntu x64] | |||

* [https://wiki.pine64.org/wiki/File:Ox64_BL808UART_connect.pdf Ox64 UART Flashing Guide] [https://gist.github.com/lupyuen/7a0c697b89abccda8e38b33dfe5ebaff (Notes)] | |||

* [https://github.com/lupyuen/lupyuen.github.io/releases/download/ox64/bl808_demo_event.bin BL808 Demo Firmware: bl808_demo_event.bin] [https://gist.github.com/lupyuen/7a0c697b89abccda8e38b33dfe5ebaff (Notes)] | |||

* [https://github.com/lupyuen/lupyuen.github.io/releases/download/ox64/whole_flash_data.bin BL808 UART Log Firmware: whole_flash_data.bin] [https://gist.github.com/lupyuen/7a0c697b89abccda8e38b33dfe5ebaff (Notes)] | |||

* [https://github.com/lupyuen/lupyuen.github.io/releases/download/ox64/BL808.DVK.Quick.Start.pdf BL808 DVK Quick Start] | |||

* [https://github.com/bouffalolab/bl808_linux/tree/main/opensbi-0.6-808 OpenSBI for BL808] | |||

* [https://github.com/bouffalolab/bl808-pac Rust Peripheral Access Crate (PAC) for BL808] | |||

* [https://github.com/bouffalolab/bl808-pac/blob/main/bl808.svd System View Description (SVD) for BL808] | |||

| Line 64: | Line 80: | ||

=== Expansion Ports === | === Expansion Ports === | ||

* USB 2.0 OTG port | * USB 2.0 OTG port | ||

* 26 GPIO Pins, | * 26 GPIO Pins, including SPI, I2C and UART functionality. Possible I2S and GMII expansion | ||

* Dual lane MiPi CSI port, | * Dual lane MiPi CSI port, located at USB-C port, for camera module | ||

=== Audio === | === Audio === | ||

| Line 76: | Line 92: | ||

* Input Power: 5V 0.5A microSD or USB-C port | * Input Power: 5V 0.5A microSD or USB-C port | ||

* Schematic: | * Schematic: | ||

** [https://files.pine64.org/doc/ox64/PINE64_Ox64-Schematic-202221007.pdf Ox64 Schematic 20221007 v1.0 ( | ** [https://files.pine64.org/doc/ox64/PINE64_Ox64-Schematic-202221007.pdf Ox64 Schematic 20221007 v1.0] | ||

** [https://files.pine64.org/doc/ox64/PINE64_Ox64_PCB_Placement-20221007.pdf Ox64 PCB Component placement 20221007 v1.0 | ** [https://files.pine64.org/doc/ox64/PINE64_Ox64_PCB_Placement-Top-20221007.pdf Ox64 PCB Component placement(ToP) 20221007 v1.0] | ||

** [https://files.pine64.org/doc/ox64/PINE64_Ox64_PCB_Placement-Bottom-20221007.pdf Ox64 PCB Component placement(Bottom) 20221007 v1.0] | |||

* Certifications: | * Certifications: | ||

** Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary. However, PINE64 still submits the SBC for FCC, CE, and ROHS certifications and obtain the certificates to prove that the SBC board can pass the testing. Please note, a final commercial product needs to perform its own testing and obtain its own certificate. | ** Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary. However, PINE64 still submits the SBC for FCC, CE, and ROHS certifications and obtain the certificates to prove that the SBC board can pass the testing. Please note, a final commercial product needs to perform its own testing and obtain its own certificate. | ||

| Line 83: | Line 100: | ||

== Datasheets for Components and Peripherals == | == Datasheets for Components and Peripherals == | ||

* | * Bouffalo BL808 SoC information: | ||

** [https://files.pine64.org/doc/datasheet/ox64/BL808_DS_en_1.1(open).pdf Bouffalo Lab BL808 SoC Datasheet] | ** [https://files.pine64.org/doc/datasheet/ox64/BL808_DS_en_1.1(open).pdf Bouffalo Lab BL808 SoC Datasheet] | ||

** [https://files.pine64.org/doc/datasheet/ox64/BL808_RM_en_1.0(open).pdf Bouffalo Lab BL808 SoC Reference Manual] | ** [https://files.pine64.org/doc/datasheet/ox64/BL808_RM_en_1.0(open).pdf Bouffalo Lab BL808 SoC Reference Manual] | ||

* SPI NOR Flash information: | * SPI NOR Flash information: | ||

** [https://files.pine64.org/doc/datasheet/star64/gd25lq128e_rev1.0_20210513.pdf | ** [https://files.pine64.org/doc/datasheet/ox64/gd25lq16e_rev1.2_20210108.pdf GigaDevice 16Mb XSPI-Flash Datasheet] | ||

** [https://files.pine64.org/doc/datasheet/star64/gd25lq128e_rev1.0_20210513.pdf GigaDevice 128Mb XSPI-Flash Datasheet] | |||

* Power Regulator information: | * Power Regulator information: | ||

** [https://files.pine64.org/doc/datasheet/ox64/IA2014-03.pdf Innovation Analog Tech IA2014 Step_down Converter Datasheet] | ** [https://files.pine64.org/doc/datasheet/ox64/IA2014-03.pdf Innovation Analog Tech IA2014 Step_down Converter Datasheet] | ||

== Articles and Blogs == | |||

* [https://gist.github.com/lupyuen/7a0c697b89abccda8e38b33dfe5ebaff First Batch of Ox64 won't appear as USB Serial Port] | |||

* [https://gist.github.com/lupyuen/2087e9b3fb40aab5e0795bb02a265a3b First Batch of Ox64 tested OK with CH340C/G] | |||

* [https://www.robertlipe.com/bl808-not-symmetric/ First thoughts on the (a)symmetery of Bouffalo Labs BL808 as in Pine64’s Ox64] | |||

== Development Efforts == | |||

* [https://twitter.com/gamelaster/status/1583916501400068096 Ox64 boots Linux successfully] | |||

* [https://twitter.com/btashton/status/1586381334439923713?t=w5xRRUR74HGK2O1Zg_aFyw&s=19 Brennan Ashton is porting Apache NuttX RTOS and OpenAMP (Asymmetric Multiprocessing) to BL808] | |||

* [https://twitter.com/thanos_engine/status/1585153938092761093 Phone Concept for BL808] | |||

[[Category:Ox64]] [[Category:Bouffalo BL808]] | [[Category:Ox64]] [[Category:Bouffalo BL808]] | ||

Revision as of 02:02, 31 October 2022

The Ox64 is a RISC-V based Single Board Computer powered by Bouffalo Lab BL808 C906 64-Bit RISC-V CPU, 32-Bit CPU, embedded 64MB PSRAM memory and build-on 3 radio RF (Wifi, BT, Zigbee). It provides breadboard friendly form factor, MicroSD Card slot, USB 2.0, and many other peripheral interfaces for makers to integrate with sensors and other devices.

Software Releases

Quick Links to the Source of OS Images Build

OS images are still in alpha build which are only fit for board bring up and testing purposes.

- Linux for BL808

- Installation Instructions for Linux on BL808 (Chinese)

- Installation Instructions for Linux on BL808 (English Auto-Translation)

- Toolchain:

- elf_newlib_toolchain/bin/riscv64-unknown-elf-gcc (Xuantie-900 elf newlib gcc Toolchain V2.2.5 B-20220323) 10.2.0

- linux_toolchain/bin/riscv64-unknown-linux-gnu-gcc (Xuantie-900 linux-5.10.4 glibc gcc Toolchain V2.2.4 B-20211227) 10.2.0

- cmake version 3.19.3

Software Development Kits

- BL808 MCU SDK

- BLDevCube Flashing Tool for Windows, macOS and Ubuntu x64

- Ox64 UART Flashing Guide (Notes)

- BL808 Demo Firmware: bl808_demo_event.bin (Notes)

- BL808 UART Log Firmware: whole_flash_data.bin (Notes)

- BL808 DVK Quick Start

- OpenSBI for BL808

- Rust Peripheral Access Crate (PAC) for BL808

- System View Description (SVD) for BL808

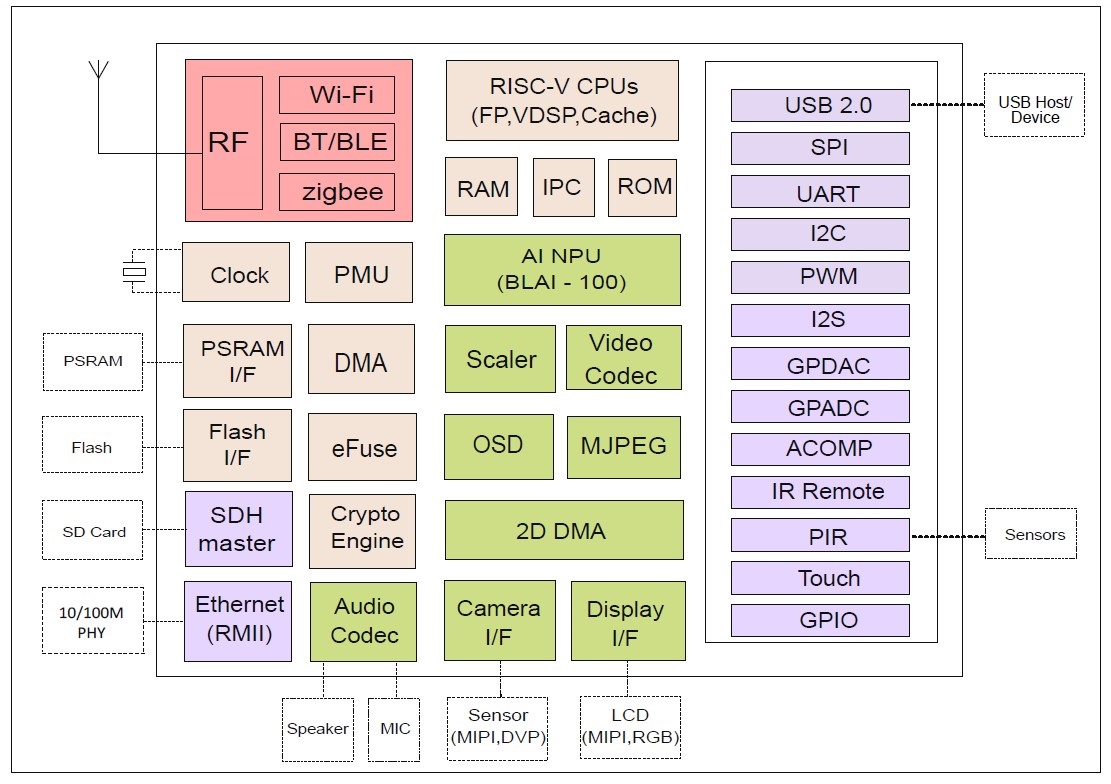

SoC and Memory Specification

- Based on Bouffalo Lab BL808

CPU Architecture

- Supports RISC-V RV64IMAFCV instruction architecture

- Five-stage single-issue sequentially executed pipeline

- Level-1 instruction and data cache of Harvard architecture, with a size of 32 KB and a cache line of 64B

- Sv39 memory management unit, realizing the conversion of virtual and real addresses and memory management

- jTLB that supports 128 entries

- Supports AXI 4.0 128-bit master interface

- Supports core local interrupt (CLINT) and platform-level interrupt controller (PLIC)

- With 80 external interrupt sources, 3 bits for configuring interrupt priority

- Supports BHT (8K) and BTB

- Compatible with RISC-V PMP, 8 configurable areas

- Supports hardware performance monitor (HPM) units

- T_head E907 320MHz 32-bit RISC-V CPU

- Supports RISC-V RV32IMAFCP instruction set

- Supports RISC-V 32-bit/16-bit mixed instruction set

- Supports RISC-V machine mode and user mode

- Thirty-two 32-bit integer general purpose registers (GPR) and thirty-two 32-bit/64-bit floating-point GPRs

- Integer (5-stage)/floating-point (7-stage), single-issue, sequentially executed pipeline

- Supports AXI 4.0 main device interface and AHB 5.0 peripheral interface

- 32K instruction cache, two-way set associative structure

- 16K data cache, two-way set associative structure

System Memory

- Embedded 64MB PSRAM

Board Features

Network

- 2.4GHz 1T1R WiFi 802.11 b/g/n

- Bluetooth 5.2

- Zigbee

- 10/100Mbps Ethernet (optional, on expansion board)

Storage

- on-board 16Mb (2MB) or 128Mb (16MB) XSPI NOR flash memory

- microSD - supports SDHC and SDXC

Expansion Ports

- USB 2.0 OTG port

- 26 GPIO Pins, including SPI, I2C and UART functionality. Possible I2S and GMII expansion

- Dual lane MiPi CSI port, located at USB-C port, for camera module

Audio

- mic (optional, on camera module)

- speaker (optional, on camera module)

Board Information, Schematics and Certifications

- Baseboard Dimensions: 51mm x 21mm x 19mm x 3.5mm (Breadboard friendly)

- Input Power: 5V 0.5A microSD or USB-C port

- Schematic:

- Certifications:

- Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary. However, PINE64 still submits the SBC for FCC, CE, and ROHS certifications and obtain the certificates to prove that the SBC board can pass the testing. Please note, a final commercial product needs to perform its own testing and obtain its own certificate.

- Not yet available

Datasheets for Components and Peripherals

- Bouffalo BL808 SoC information:

- SPI NOR Flash information:

- Power Regulator information:

Articles and Blogs

- First Batch of Ox64 won't appear as USB Serial Port

- First Batch of Ox64 tested OK with CH340C/G

- First thoughts on the (a)symmetery of Bouffalo Labs BL808 as in Pine64’s Ox64