Difference between revisions of "PineCone"

Jump to navigation

Jump to search

| Line 20: | Line 20: | ||

** Secure boot | ** Secure boot | ||

** Secure debug | ** Secure debug | ||

** AES 128/192/256 | ** AES 128/192/256 | ||

** SHA-1/224/256 | ** SHA-1/224/256 | ||

Revision as of 02:16, 30 November 2020

Page under construction, information subject to change.

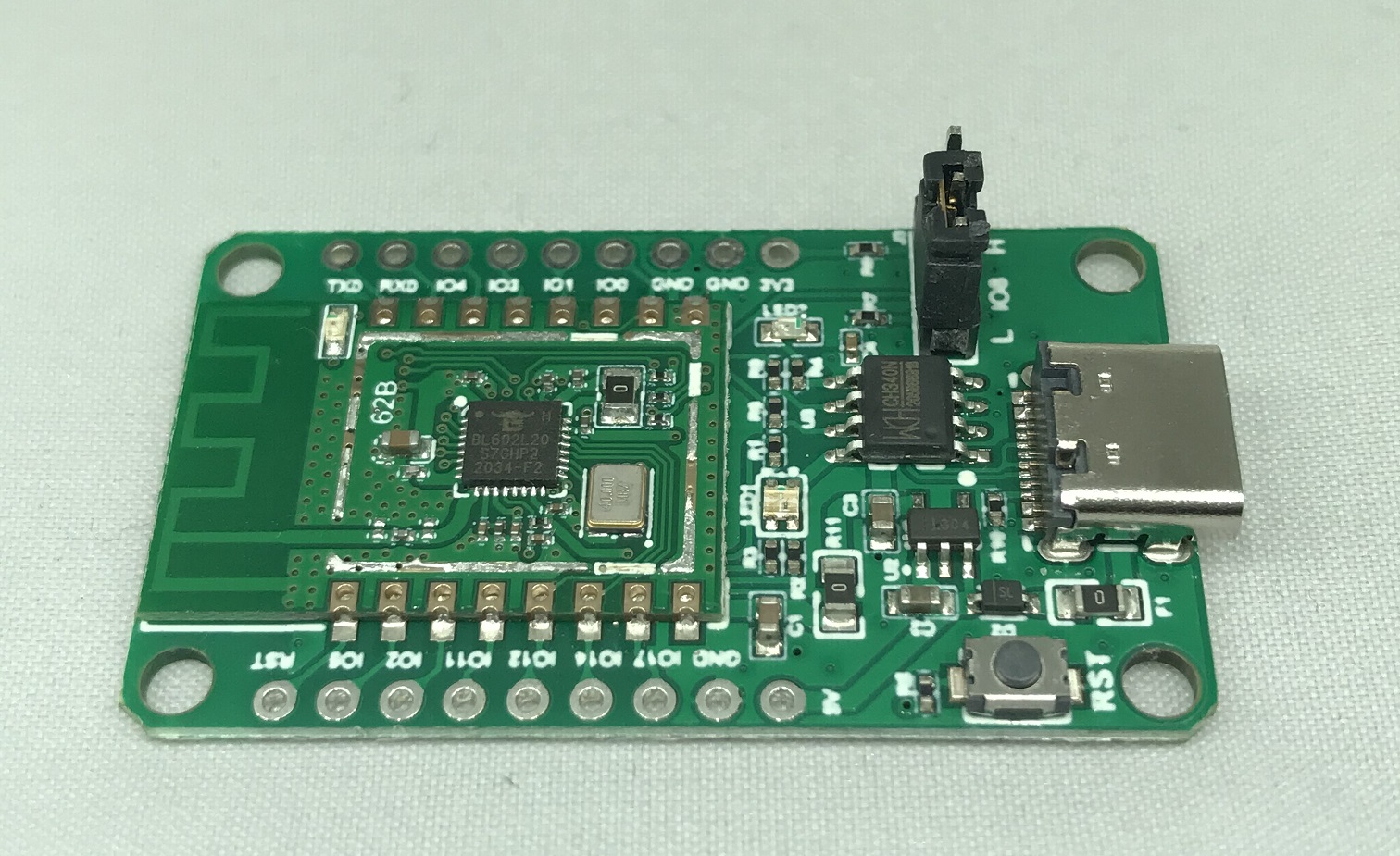

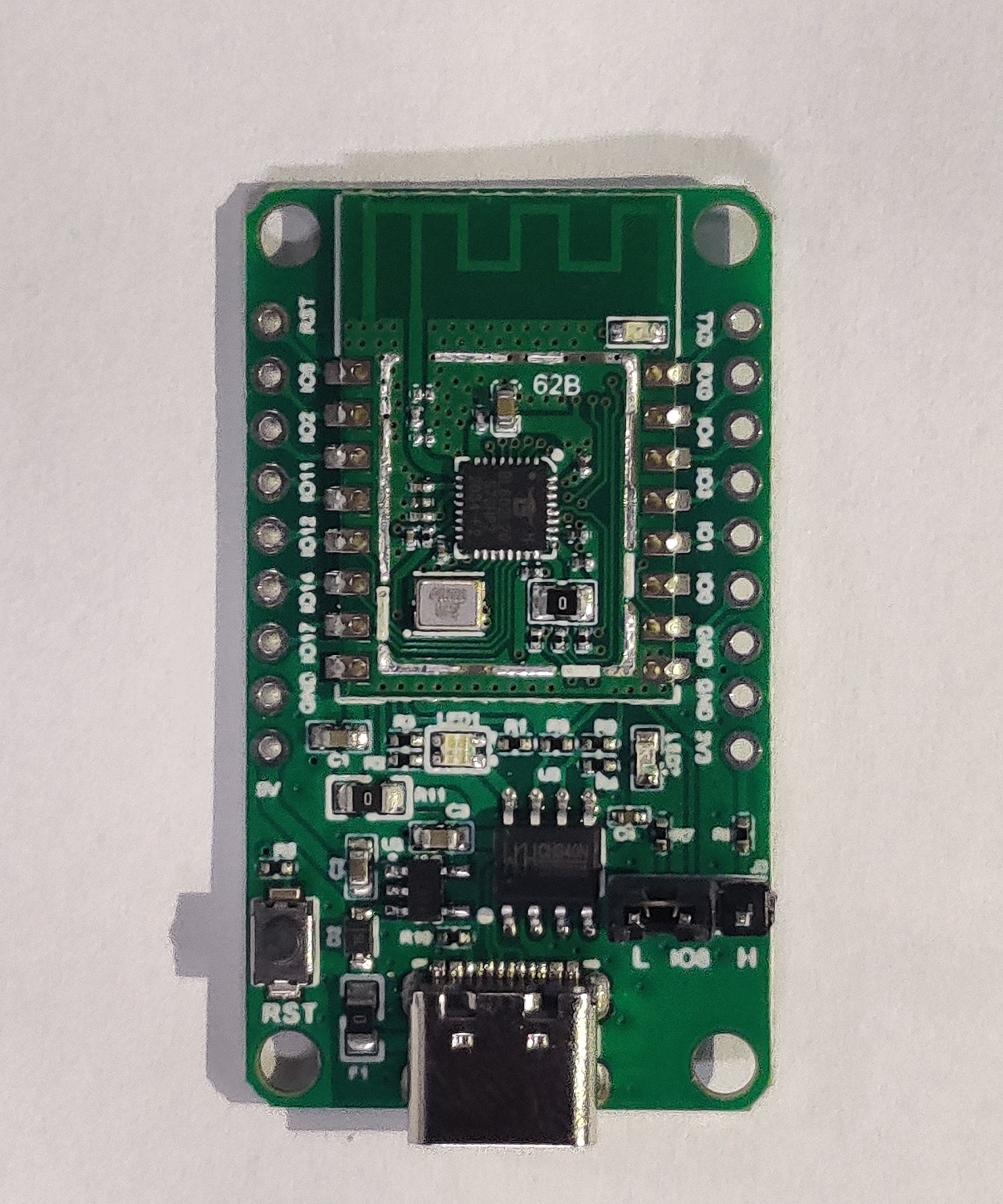

- PineCone BL-602 EVB (Evaluation Board):

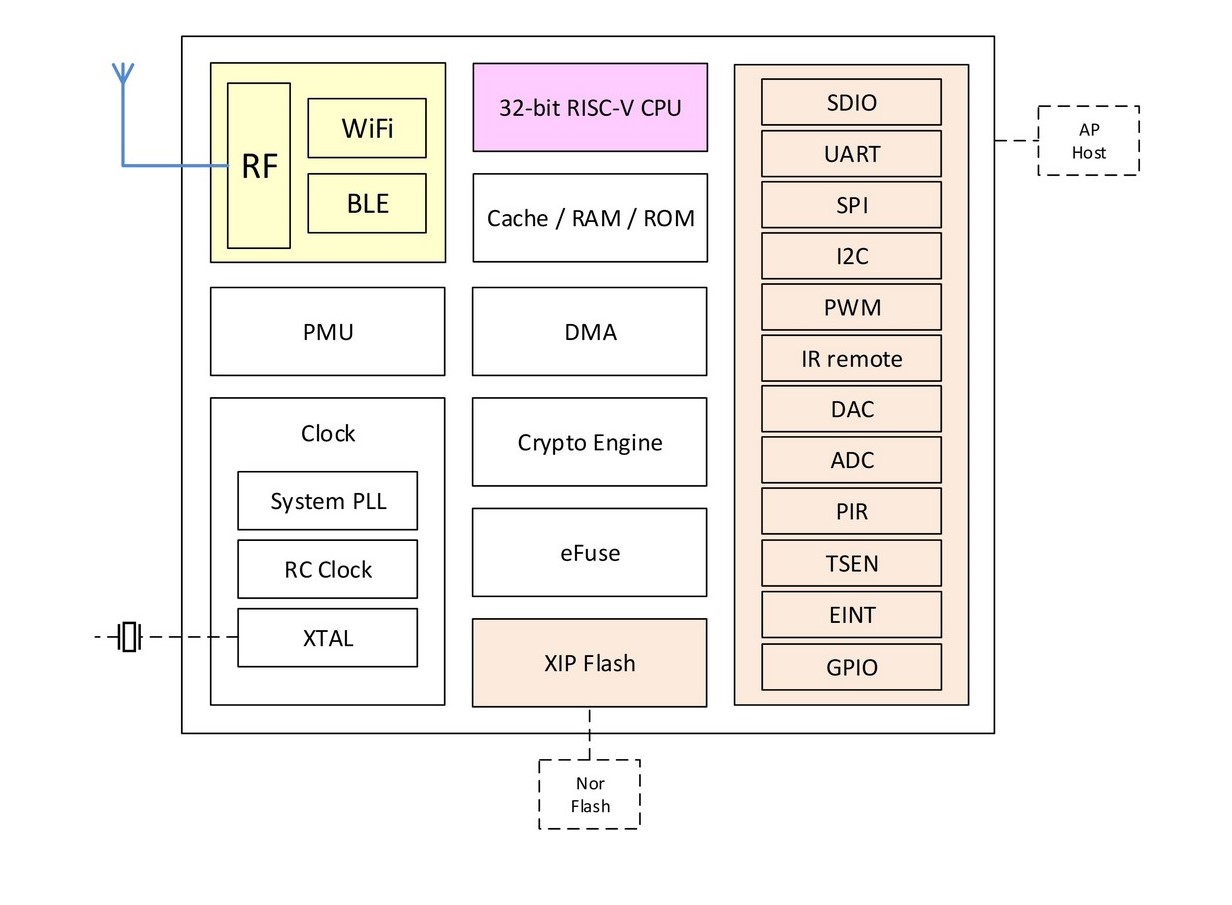

BL602 Specifications

- CPU: 32-bit RV32IMAFC RISC-V “SiFive E24 Core”

- Memory:

- 128KB ROM

- 276KB SRAM

- 1Kb eFuse

- 2MB Embedded Flash

- Security:

- Secure boot

- Secure debug

- AES 128/192/256

- SHA-1/224/256

- TRNG (True Random Number Generator)

- PKA (Public Key Accelerator)

- Wireless:

- Wi-Fi 802.11 b/g/n

- Bluetooth® Low Energy 5.0

- Wi-Fi Fast connection with BLE assistance

- Wi-Fi and BLE coexistence

- Wi-Fi Security WPS/WEP/WPA/WPA2/WPA3

- STA, SoftAP and sniffer modes

- Multi-Cloud connectivity

- 2.4 GHz RF transceiver

- Integrated RF balun, PA/LNA

- Package Type:

- 32 pin QFN 4mm x 4mm

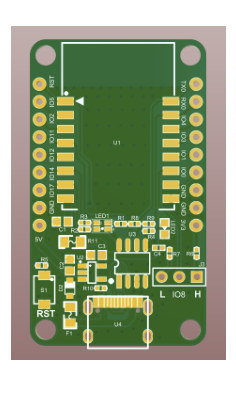

PineCone BL602 EVB information and schematics

- Approximate dimensions: 26mm x 43mm

- Board layout:

- PineCone BL602 EVB schematic ver 1.1

- Note: Current schematic, cc1 and cc2 share one 5.1KOhm resistor. Next schematic design will separate out the cc1 and cc2 has it own 5.1KOhm resistors

Datasheets for components and peripherals

- Bouffalo BL-602 SoC information:

- Bouffalo Lab BL602 SoC Datasheet V1.2

- Bouffalo Lab BL602 SoC Datasheet V1.1

- Bouffalo Lab BL602 SoC Reference Manual V1.1

- Please note that the Chinese wording "寄存器描述" means "Register Description" in reference manual ver 1.1

Misc notes

Planned to be available in at least three form factors:

- NUT-01S -> ESP-01S

- NUT-12S -> ESP-12S

- NUT-15 -> RTL8723/AMPAK