Difference between revisions of "Oz64"

| (21 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

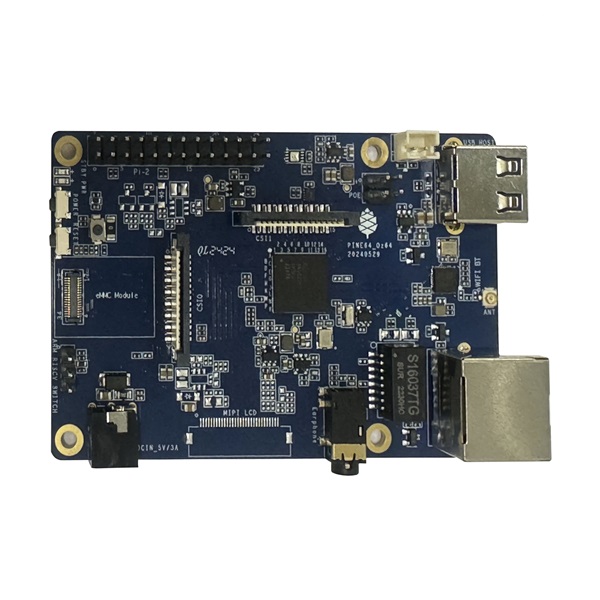

[[File:Oz64_3D_model.png|thumb|right|The | [[File:Oz64_SBC_600x600.jpg|thumb|right|The Oz64 SBC]] | ||

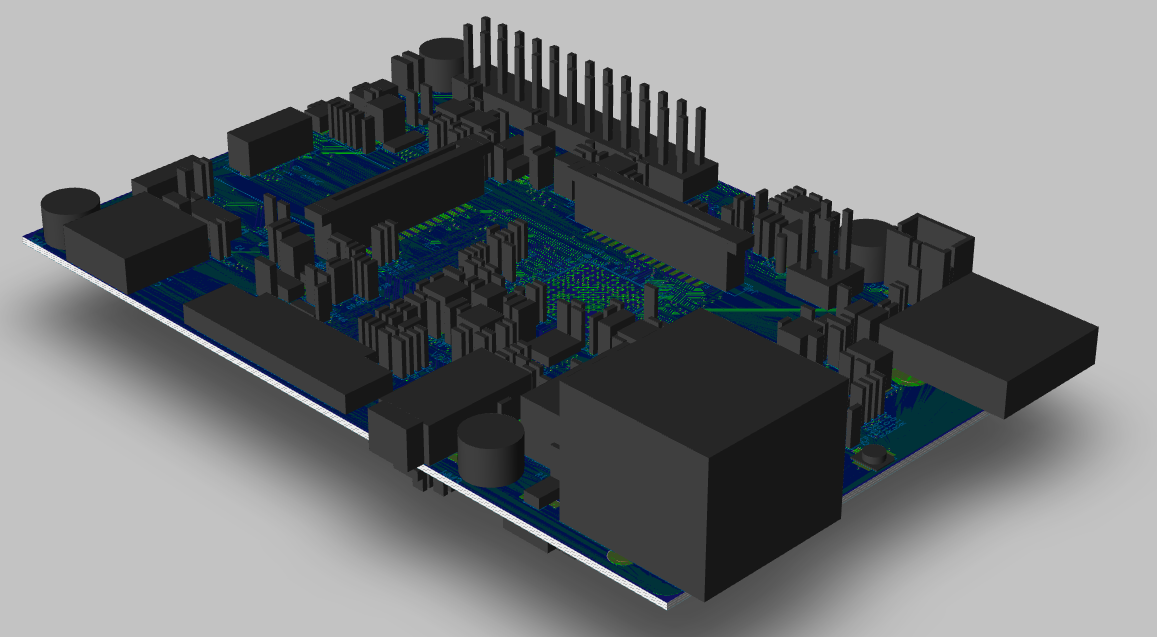

[[File:RISC-V.png|thumb|right | [[File:Oz64_3D_model.png|thumb|right|The Oz64 3D model]] | ||

[[File:RISC-V.png|thumb|right]] | |||

The ''' | The '''Oz64''' is a low cost single-board computer based on the Sophgo SG2000 SoC with dual T-Head C906 64-bit RISC-V cores, an ARM Cortex A53 64-bit RISC CPU core and an 8051 8-bit core supported by 512 MB of embedded DRAM memory, with WiFi and Bluetooh radio interfaces. The Oz64 SBC comes in a model-B form-factor, has a microSD card slot, an eMMC plugin connector, an USB 2.0 Type-A host port, and many other peripheral interfaces for makers to integrate with sensors and other devices. | ||

== Software Releases == | == Software Releases == | ||

| Line 8: | Line 9: | ||

=== Quick Links to the Source of OS Images Build === | === Quick Links to the Source of OS Images Build === | ||

There is a community effort to bring updated kernels, peripherals and buildroot - Lots of communication happening in the # | There is a community effort to bring updated kernels, peripherals and buildroot - Lots of communication happening in the #ox64-nutcracker channel. | ||

* [https://github.com/lupyuen2/wip-nuttx/releases/download/sg2000-1/Image] | * [https://github.com/lupyuen2/wip-nuttx/releases/download/sg2000-1/Image Nuttx Released Image] by Lup Yuen | ||

Toolchain: | Toolchain: | ||

| Line 68: | Line 69: | ||

[[File:Arm-logo.png|right|200px]] | [[File:Arm-logo.png|right|200px]] | ||

ARM Cortex-A53 | ARM Cortex-A53 1GHz 64-bit RISC CPU: | ||

* [https://www.arm.com/products/processors/cortex-a/cortex-a53-processor.php Quad-core Cortex-A53 up to 1.0GHz CPU] | * [https://www.arm.com/products/processors/cortex-a/cortex-a53-processor.php Quad-core Cortex-A53 up to 1.0GHz CPU] | ||

| Line 102: | Line 103: | ||

* USB 2.0 Host port | * USB 2.0 Host port | ||

* 26 GPIO pins, including SPI, I<sup>2</sup>C and UART functionality | * 26 GPIO pins, including SPI, I<sup>2</sup>C and UART functionality | ||

* Dual-lane MiPi CSI port | * 2x Dual-lane MiPi CSI port | ||

* | * Optional dual-lane MiPi DSI port | ||

== Board Information, Schematics and Certifications == | == Board Information, Schematics and Certifications == | ||

| Line 109: | Line 110: | ||

Board Dimensions: 85mm x 56mm x 18.8mm, see the [https://files.pine64.org/doc/rock64/rock64%20board%20dimension.pdf model-B board dimension drawing] | Board Dimensions: 85mm x 56mm x 18.8mm, see the [https://files.pine64.org/doc/rock64/rock64%20board%20dimension.pdf model-B board dimension drawing] | ||

Input Power: +5V @2A with 3.5mm/1.35mm Type H Barrel type DC connector (@ | Input Power: +5V @2A with 3.5mm/1.35mm Type H Barrel type DC connector (@1.5A will work if there is no heavy load on the USB 2.0 port) | ||

Pre-Production version schematic: | Pre-Production version schematic: | ||

* [https://files.pine64.org/doc/oz64/PINE64_Oz64_Schematic-20240517.pdf Oz64 Schematic 20240517 v1.0.0] | * [https://files.pine64.org/doc/oz64/PINE64_Oz64_Schematic-20240517.pdf Oz64 Schematic 20240517 v1.0.0] | ||

* [https://files.pine64.org/doc/oz64/ | * [https://files.pine64.org/doc/oz64/PINE64_Oz64_PCB_Placement-Top-20240517.pdf Oz64 PCB Component placement(ToP) 20240517 v1.0.0] | ||

* [https://files.pine64.org/doc/oz64/ | * [https://files.pine64.org/doc/oz64/PINE64_Oz64_PCB_Placement-Bottom-20240517.pdf Oz64 PCB Component placement(Bottom) 20240517 v1.0.0] | ||

Board Pinout Diagram: | |||

* Courtesy by [https://github.com/aisuneko @aisuneko Github site] | |||

[[File:Oz64_Board_pinout_by_aisuneko.png|800px]] | |||

Certifications: | Certifications: | ||

* Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary. | * Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary. | ||

== Datasheets for Components and Peripherals == | == Datasheets for Components and Peripherals == | ||

| Line 126: | Line 133: | ||

Wifi/BT information: | Wifi/BT information: | ||

* [https://files.pine64.org/doc/datasheet/ | * [https://files.pine64.org/doc/datasheet/oz64/AIC8800DC%20Datasheet%20v1.0.pdf AIC Semi AIC8800DC Datasheet] | ||

Power Regulator information: | Power Regulator information: | ||

* [https://files.pine64.org/doc/datasheet/ | * [https://files.pine64.org/doc/datasheet/oz64/ETA3414_V1.6.pdf Empower ETA3414 1.5A 3MHz Step_down Converter Datasheet] | ||

* [https://files.pine64.org/doc/datasheet/oz64/ETA3418_V1.4.pdf Empower ETA3418 2.5A 3MHz Step_down Converter Datasheet] | |||

* [https://files.pine64.org/doc/datasheet/oz64/ETA5050_V2.4.pdf Empower ETA5050 500mA Low Noise, High PSRR, Fast Transient Response LDO Datasheet] | |||

MicroSD socket information: | MicroSD socket information: | ||

* [https://files.pine64.org/doc/datasheet/ox64/TF%20PUSH%20type%20socket%20specification.pdf Push type microSD socket specification] | * [https://files.pine64.org/doc/datasheet/ox64/TF%20PUSH%20type%20socket%20specification.pdf Push type microSD socket specification] | ||

== Resources and Articles == | |||

== | == Development Efforts == | ||

== Build== | |||

* [https://lupyuen.github.io/articles/sg2000#appendix-build-nuttx-for-sg2000 Nuttx Build] by Lup Yuen | |||

[[Category:Oz64]] | [[Category:Oz64]] | ||

[[Category:Sophgo SG2000]] | [[Category:Sophgo SG2000]] | ||

Latest revision as of 03:45, 20 May 2025

The Oz64 is a low cost single-board computer based on the Sophgo SG2000 SoC with dual T-Head C906 64-bit RISC-V cores, an ARM Cortex A53 64-bit RISC CPU core and an 8051 8-bit core supported by 512 MB of embedded DRAM memory, with WiFi and Bluetooh radio interfaces. The Oz64 SBC comes in a model-B form-factor, has a microSD card slot, an eMMC plugin connector, an USB 2.0 Type-A host port, and many other peripheral interfaces for makers to integrate with sensors and other devices.

Software Releases

Quick Links to the Source of OS Images Build

There is a community effort to bring updated kernels, peripherals and buildroot - Lots of communication happening in the #ox64-nutcracker channel.

- Nuttx Released Image by Lup Yuen

Toolchain:

- elf_newlib_toolchain/bin/riscv64-unknown-elf-gcc (Xuantie-900 elf newlib gcc Toolchain V2.2.5 B-20220323) 10.2.0

- linux_toolchain/bin/riscv64-unknown-linux-gnu-gcc (Xuantie-900 linux-5.10.4 glibc gcc Toolchain V2.2.4 B-20211227) 10.2.0

- cmake version 3.19.3

Software Development Kits

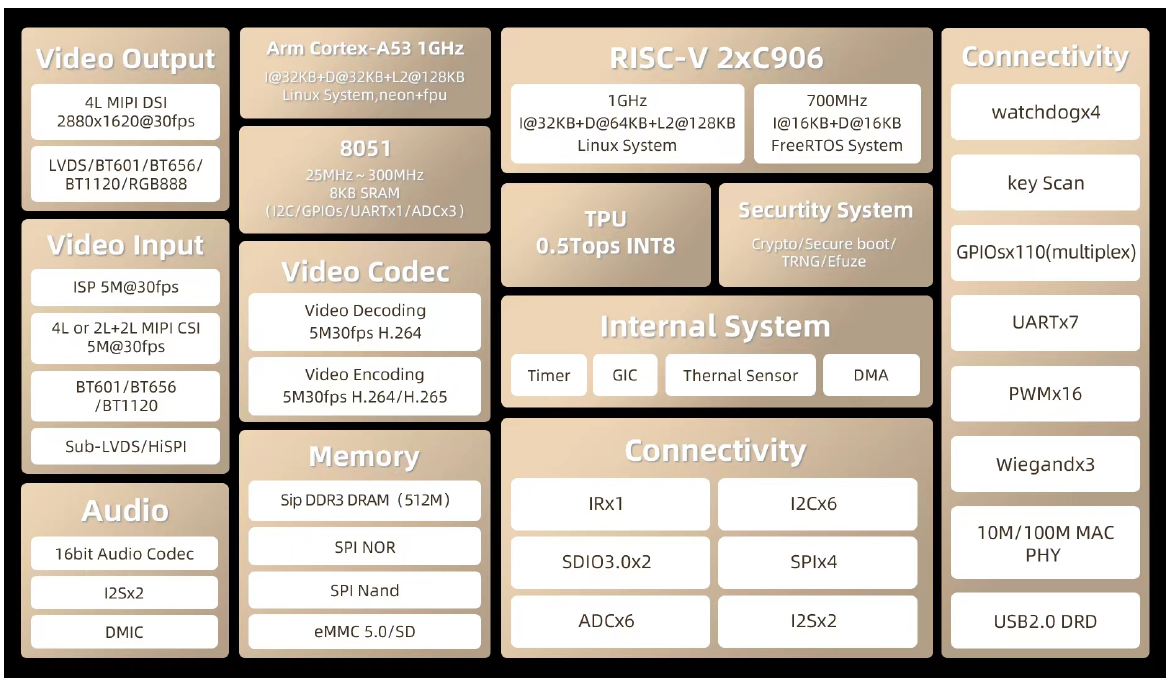

SoC and Memory Specification

Based on the Sophgo SG-200x

CPU Architecture

T-Head C906 1GHz MHz 64-bit RISC-V CPU:

- Supports RISC-V RV64IMAFCV instruction architecture

- Five-stage single-issue sequentially executed pipeline

- Level-1 instruction and data cache of Harvard architecture, with a size of 32 KB and a cache line of 64KB

- Level-2 128KB cache

- Sv39 memory management unit, realizing the conversion of virtual and real addresses and memory management

- jTLB that supports 128 entries

- Supports AXI 4.0 128-bit master interface

- Supports core local interrupt (CLINT) and platform-level interrupt controller (PLIC)

- With 80 external interrupt sources, 3 bits for configuring interrupt priority

- Supports BHT (8K) and BTB

- Compatible with RISC-V PMP, 8 configurable areas

- Supports hardware performance monitor (HPM) units

- See here

T-Head C906 700Mhz MHz 64-bit RISC-V CPU:

- Supports RISC-V RV64IMAFCV instruction architecture

- Five-stage single-issue sequentially executed pipeline

- Level-1 instruction and data cache of Harvard architecture, with a size of 16 KB and a cache line of 16KB

- Sv39 memory management unit, realizing the conversion of virtual and real addresses and memory management

- jTLB that supports 128 entries

- Supports AXI 4.0 128-bit master interface

- Supports core local interrupt (CLINT) and platform-level interrupt controller (PLIC)

- With 80 external interrupt sources, 3 bits for configuring interrupt priority

- Supports BHT (8K) and BTB

- Compatible with RISC-V PMP, 8 configurable areas

- Supports hardware performance monitor (HPM) units

- See here

ARM Cortex-A53 1GHz 64-bit RISC CPU:

- Quad-core Cortex-A53 up to 1.0GHz CPU

- Full implementation of the ARM architecture v8-A instruction set

- ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

- ARMv8 Cryptography Extensions

- In-order pipeline with symmetric dual-issue of most instructions

- Unified system L2 128KB cache

- Includes VFP v3 hardware to support single and double-precision operations

- Integrated 32KB L1 instruction cache, 32KB 4-way set associative L1 data cache

- TrustZone technology support

- PD_A53: Cortex-A53 + Neon + FPU + L1 I/D Cache of core 2/3

8051 25-300MHz 8-bit CPU:

- Integrated 8K SRAM

System Memory

- SIP DRAM 512MB

Board Features

Network

- 2.4 GHz 1T1R WiFi6

- Bluetooth 5.2

- 10/100 Mbit/s Ethernet with optional PoE capability

Storage

- On-board eMMC module socket

- MicroSD, supports SDHC and SDXC

Expansion Ports

- USB 2.0 Host port

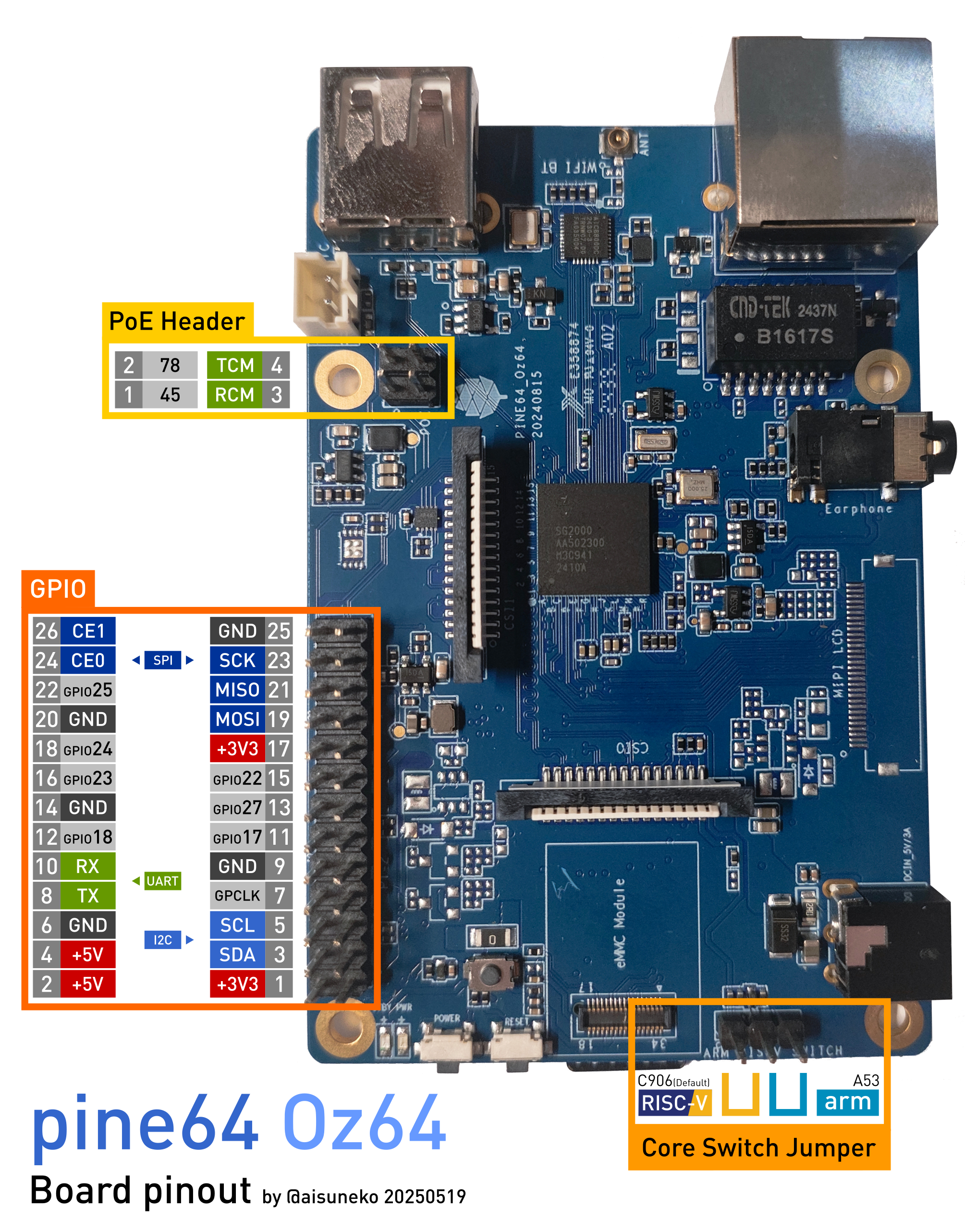

- 26 GPIO pins, including SPI, I2C and UART functionality

- 2x Dual-lane MiPi CSI port

- Optional dual-lane MiPi DSI port

Board Information, Schematics and Certifications

Board Dimensions: 85mm x 56mm x 18.8mm, see the model-B board dimension drawing

Input Power: +5V @2A with 3.5mm/1.35mm Type H Barrel type DC connector (@1.5A will work if there is no heavy load on the USB 2.0 port)

Pre-Production version schematic:

- Oz64 Schematic 20240517 v1.0.0

- Oz64 PCB Component placement(ToP) 20240517 v1.0.0

- Oz64 PCB Component placement(Bottom) 20240517 v1.0.0

Board Pinout Diagram:

- Courtesy by @aisuneko Github site

Certifications:

- Disclaimer: Please note that PINE64 SBC is not a "final" product and in general certification is not necessary.

Datasheets for Components and Peripherals

Sophgo SG2000 SoC information:

Wifi/BT information:

Power Regulator information:

- Empower ETA3414 1.5A 3MHz Step_down Converter Datasheet

- Empower ETA3418 2.5A 3MHz Step_down Converter Datasheet

- Empower ETA5050 500mA Low Noise, High PSRR, Fast Transient Response LDO Datasheet

MicroSD socket information:

Resources and Articles

Development Efforts

Build

- Nuttx Build by Lup Yuen